Arm ist die derzeit dominierende CPU-Architektur für Mikrocontroller und Mikroprozessoren für kleine sowie mobile Geräte. Die Gründe hierfür sind, dass Arm-Chips einen reduzierten und dadurch effizienten Befehlssatz (RISC) verwenden, während die Architektur der Intel und der meisten AMD-Chips x86 den komplexen Befehlssatz (CISC) nutzt.

Die Unterschiede zwischen den Ansätzen RISC und CISC

RISC und CISC sind zwei unterschiedliche Befehlssatzarchitekturen (Instruction Set Architectures, ISAs).

RISC – Reduced Instruction Set Computer

Die RISC-Architektur zielt darauf ab, die Komplexität der Befehle zu verringern und einfache, aber leistungsfähige Befehle zu liefern, die innerhalb eines Zyklus mit hoher Taktfrequenz ausgeführt werden.

Die Verringerung der Komplexität des von der Hardware ausgeführten Befehlssatzes ebnet den Weg für einen effizienten Chip (in Bezug auf den Energieverbrauch). Dies ist insbesondere für mobile Hardware, die über einen Akku betrieben wird, wichtig.

CISC – Complex Instruction Set Computer

CISC ist der Urvater des CPU-Designs. Die CISC-Architektur zielt darauf ab, die Anzahl der Anweisungen pro Programm zu verringern und gleichzeitig die Anzahl der Zyklen pro Anweisung zu erhöhen.

CPUs mit CISC-Architektur können viele Operationen in einem einzigen komplexen Befehl ausführen. Der Befehl benötigt jedoch mehrere Zyklen zur Ausführung und erfordert eine Menge Schaltungen in der CPU.

RISC scheint sich im Bereich (Desktop-)Computing zu etablieren

Anfangs von vielen belächelt und im Rahmen von „Windows auf Arm“ schon beinahe als gescheitert erklärt, hat sich RISC spätestens seit Apple im Jahr 2020 seine eigenen, auf Arm basierenden M1-Chip für ihre Macintosh-Computer vorgestellt hat, als starker Konkurrent von x86 gemausert. Viele glauben daran, dass RISC die CPU-Architektur ist, die aufgrund ihrer Effizienz, mittelfristig der CISC-Architektur den Rang im Bereich des Anwender-Computings ablaufen wird.

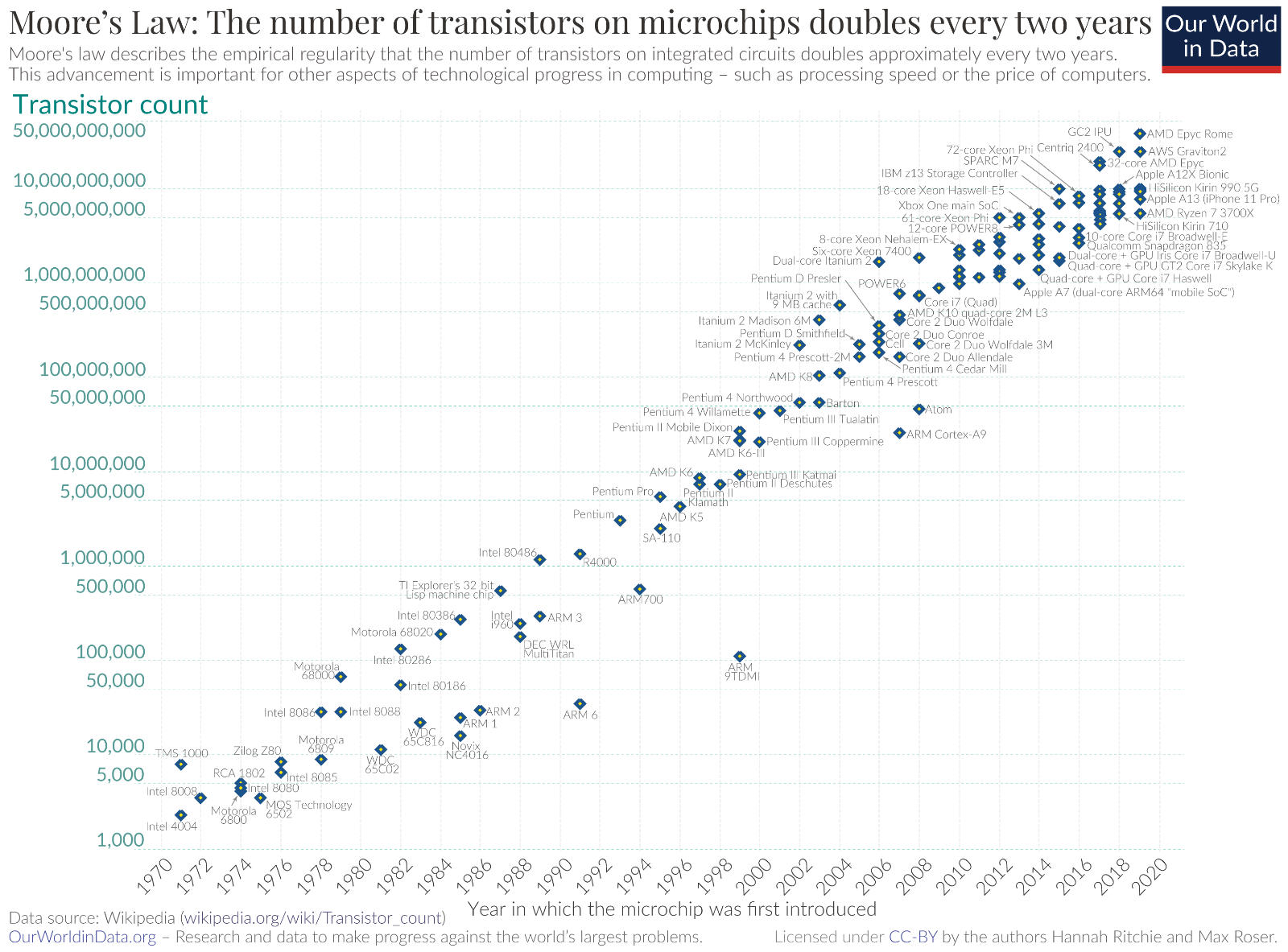

Nach dem Mooreschen Gesetz verdoppelt sich die Zahl der Transistoren auf einem Mikrochip alle zwei Jahre, und die Kosten halbieren sich. Bei der Entwicklung von CISC besteht aufgrund der größeren Komplexität der Hardware immer ein hohes Ausfallrisiko. Außerdem dauert es in der Regel länger, eine neue CISC-Architektur zu entwickeln.

Auf der anderen Seite ist RISC eine einfache Architektur, die leichter zu implementieren ist. Das bedeutet, dass sie in kürzerer Zeit auf den Markt kommen kann und somit ein geringeres Risiko für die Entwicklungskosten aufweist. Aus diesem Grund kann RISC auch als die unvermeidliche Konsequenz des Mooreschen Gesetzes gesehen werden.

Die Nummer der Transistoren in Mikrochips zwischen 1970 – 2020

Arm als Marktführer im Bereich RISC-Chips könnte jedoch in naher Zukunft ernsthafte Konkurrenz von einer vergleichsweise neuen RISC-Prozessorarchitektur bekommen. RISC-V.

Was sind die Hauptunterschiede zwischen RISC-V und Arm, und könnte sich die eine gegenüber der anderen durchsetzen?

Was steckt hinter RISC-V?

Einfach ausgedrückt ist RISC-V (römisch fünf) eine neue quelloffene ISA (Befehlssatzarchitektur), die zu Forschungs- und Ausbildungszwecken im Jahr 2010 an der University of California in Berkeley entwickelt wurde.

Die RISC-V-Befehlssatzarchitektur wird mit einem Basis-ISA geliefert, der für Ausbildungszwecke verwendet und angepasst werden kann. Die Benutzer können jedoch auch nach Belieben optionale Erweiterungen hinzufügen, um den Prozessorkern leistungsfähiger zu machen.

Als RISC-V ins Leben gerufen wurde, bestand das Hauptmotiv darin, die Komplexität bei der Entwicklung beliebiger Prozessorkerne zu beseitigen. Diese spezielle Hardware-Implementierung hat sich nun in eine für die Software sichtbare Schnittstelle für eine breite Palette von Implementierungen verwandelt. Damit RISC-V eine universelle ISA werden kann, sollte sie für alle Mikroprozessorarten (in-order, out-of-order, decoupled) effizient und für alle Prozessorgrößen geeignet sein.

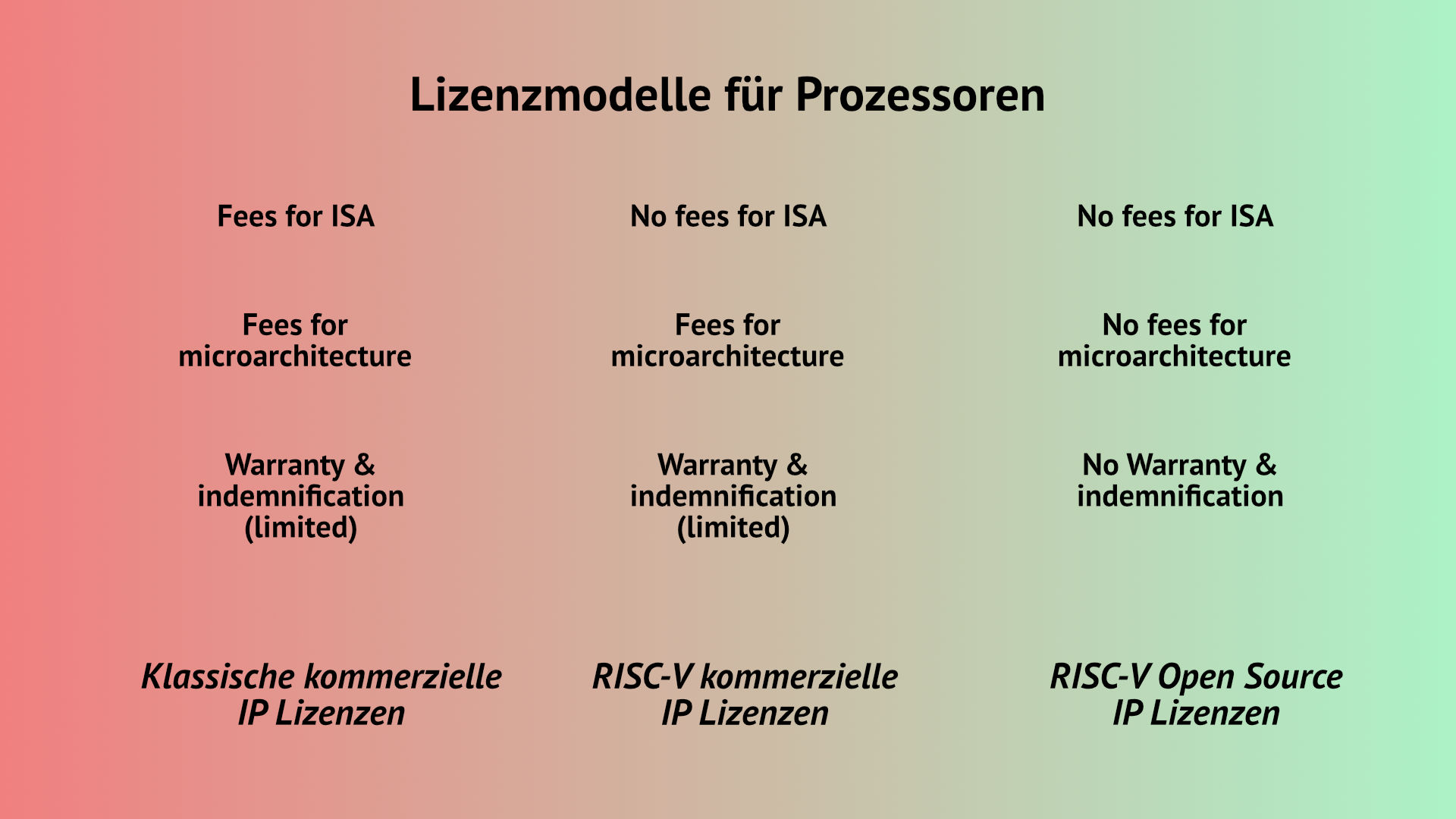

Wenn von RISC-V die Rede ist, wird immer sofort der Open-Source-Ansatz betont. In Wirklichkeit handelt es sich jedoch mittlerweile um einen „Offenen Standard“ für eine Beschreibung der Funktionsweise des Prozessordesigns. Es wird beschrieben, wie die Software mit dem Hardware-Prozessor kommuniziert, ähnlich wie bei anderen gängigen ISAs auf dem Markt. Marktfertige RISC-V Chips, wie die von SiFive, basieren somit auf einem Open Standard ISA, die keine Mikroarchitektur und kein Geschäftsmodell definiert. Die Hardware kann jedoch auch proprietär vertrieben werden. Anbieter von RISC-V Chips können ihre Chips als Gesamtpaket verkaufen oder beispielsweise ein ähnliches Lizenzierungsmodell wie ARM Ltd. anbieten.

Wenn man sich konkurrierende ISAs wie x86 oder Arm ansieht, so kann man erkennen, dass diese das Recht, Prozessorkerne zu entwickeln, aufgrund der damit verbundenen Nutzungsgebühren beschränken. Dies begrenzt nicht nur die Möglichkeiten der Chip-Weiterentwicklung, sondern bindet die Unternehmen/Kunden auch an die Chip-Anbieter. Mit einem offenen ISA wie RISC-V können innovative Prozessorhersteller nun ihre eigenen Produkte auf der Grundlage von RISC-V entwickeln und damit der Innovationen im Chip-Design einen enormen Schub verleihen.

Was sind die Unterschiede zu den Arm-Chips?

Während beide Prozessortechnologien in ihrer Grundfunktion ähnlich sind (d.h. beide sind ladungsgespeichert und verwenden RISC), besteht der Hauptunterschied zwischen RISC-V und Arm darin, dass Arm proprietär ist. Das bedeutet, dass jeder Entwickler, der eine Arm-CPU in sein Design (System on a Chip) integrieren möchte, Lizenzgebühren an ARM Ltd. zahlen muss.

RISC-V hingegen ist quelloffen und erfordert daher keine Lizenzgebühren oder Lizenzen. Dies bedeutet jedoch nicht, dass es sich nicht in jedem Fall um quelloffene Prozessoren handeln muss, sondern lediglich um eine quelloffene Spezifikation. Somit wird es Entwicklern zwar ermöglicht, kostenlos mit RISC-V zu experimentieren und RISC-V-Systeme zu entwickeln, aber es gibt wenig bis gar keine Unterstützung für das Hardware-Design. Arm hingegen verfügt über Teams von Ingenieuren, die es den Entwicklern leichter machen können, Arm-CPUs zu integrieren.

Wie Arm und x86 können auch RISC-V-Prozessorkerne kommerziell lizenzierte Kerne sein. Der Grund hierfür ist, dass RISC-V sich als offener Standard versteht.

Da die Arm-Architektur proprietär ist und es sich bei der Arm Ltd. um ein Unternehmen handelt, können Lizenzen von Regierungen gesperrt oder das Unternehmen von Konkurrenten/Investoren aufgekauft werden. Der Chip-Hersteller Nvidia steht derzeit kurz davor, Arm Ltd. zu übernehmen.

RISC-V hingegen ist quelloffen und kann von jedem genutzt werden, um ein eigenes Design zu implementieren. Dies ist einer der Gründe, warum sich beispielsweise einige chinesische Entwickler für ihre zukünftigen Designs RISC-V zuwenden.

Welches Chip-Design wird sich in Zukunft durchsetzen?

Die Verwendung und Erforschung von RISC-V nimmt zu. Große Unternehmen suchen bereits nach Alternativen zu Arm. Die Mitglieder der RISC-V Foundation lesen sich wie das Who-is-Who der weltweiten High-Tech-Unternehmen.

Da sich die Technologie weiter verbessert und die Unterstützung für RISC-V zunimmt, haben Entwickler somit die Wahl zwischen einer kostenpflichtigen Prozessorarchitektur oder einer kostenlosen Architektur ohne Einschränkungen. Der Versuch von Nvidia, Arm zu übernehmen, wird einigen auch nicht gefallen und zeigt, dass sich Abhängigkeiten sehr schnell verschieben können, ohne dass darauf eingewirkt werden kann.

Die Zukunft von RISC-V ist vielversprechend, da es von den Unternehmen angenommen und von den Universitäten unterstützt wird. In den letzten Jahren haben wir bereits einen Umbruch in der Halbleiterindustrie erlebt, der auch auf die wachsende Akzeptanz der RISC-Architektur zurückzuführen ist.

RISC-V ist wie gesagt kein offener Prozessorkern, sondern eine offene Standardspezifikation, die von jedem kostenlos übernommen werden kann. Jeder kann somit seinen eigenen Prozessorkern auf der Grundlage von RISC-V bauen und kommerziell lizenzieren. Hierdurch ist es gut möglich, dass in naher Zukunft neue Player den Markt betreten. Die Gewinner wären dann die Kunden. Also wir alle.

Fazit

Ein offener ISA-Standard bietet Flexibilität, die Möglichkeit der Anpassung und eine weltweite Zusammenarbeit, um daran zu arbeiten oder im Kollektiv Probleme zu lösen. Das ist die Power von Open Source.

Doch nur weil etwas kostenlos und quelloffen ist, heißt das nicht, dass es sich automatisch durchsetzen wird. Das Linux-Betriebssystem ist ein klassisches Beispiel; obwohl die meisten Distributionen kostenlos sind, macht Linux nur einen winzigen Prozentsatz der Desktop-Betriebssysteme in der Welt aus.

Bei den Servern hingegen ist Linux überaus erfolgreich. Zudem kann davon ausgegangen werden, dass viele Unternehmen aus unterschiedlichen Branchen daran interessiert sein dürften, einen Fuß in das lukrative und zukunftsfähige Geschäft mit Mikroprozessoren zu bekommen.

Arm ist, was die Performance angeht, RISC-V derzeit vermutlich noch ein paar Generationen voraus, aber da die ISA lizenzfrei und quelloffen ist, gibt es ein großes Interesse von Unternehmen, denn es war noch nie so einfach, einen eigenen Chip zu entwickeln. Viele Unternehmen und Institutionen haben ein Interesse daran, unabhängig von den Chip-Herstellern/Lizenzgebern zu werden.

RISC-V könnte also die nächste Revolution der Computerindustrie werden.

—

Pyngu Digital